The speed and complexity of the latest TLC and QLC flash technologies set new challenges in designing large capacity high performance SSD devices, from the hardware (signal integrity, power management) and the firmware (flash algorithms, error correction) point of view. Massive amounts of accurate data must be collected and analyzed to characterize the flash endurance, errors, defects, operation’s timing and power.

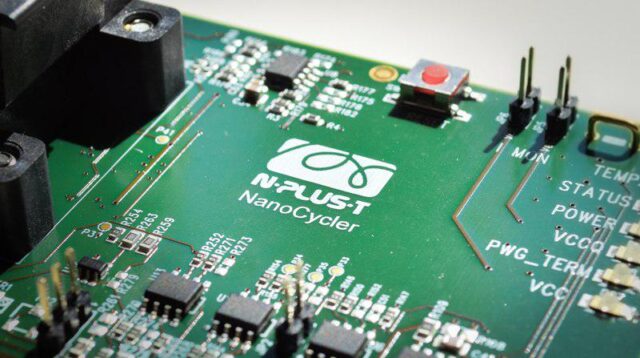

NanoCycler HS, bundled with BarnieMAT data analytics, provides the best-in-class and most cost effective solution for the exploration of the NAND memories.

NanoCycler HS:

Supports endurance and functional testing of NAND devices by providing C++ and Python API with full ONFI command set and with customizable signal sequences.

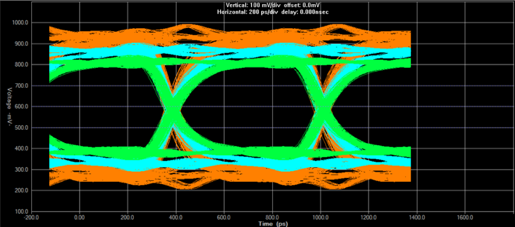

Exercises and stresses at-speed – up to 1.6 GT/sec – the devices under test faithfully replicating the use conditions of the application.

Provides high-accuracy – 10 mV precision – programmable power supplies for accurate voltage margins analysis.

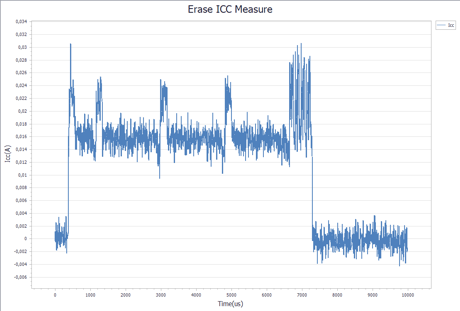

Captures the power consumption for each supply at 50 nsec sampling rate with 1 mA resolution. Flash operations power consumption data are processed in real time to provide high resolution current consumption traces, and key metrics (peak, average, distributions) over long period of time.

Characterizes the flash interface timing with 1 nsec I/O edge placement and 20 nsec flash response time acquisition.

Has a scalable and expandable architecture, from 1 to 48 test sites, to optimize cost and long term investment.

Allows full independence of the test sites where each device under test can run at individual temperature, timing, voltage levels, with different test programs.

Integrates the data analysis environment to post-process and present the results to accelerate time to product.

Highest quality characterization results at the lowest cost and effort – NanoCycler HS represents a future-safe investment to design high-performance reliable mass storage devices.